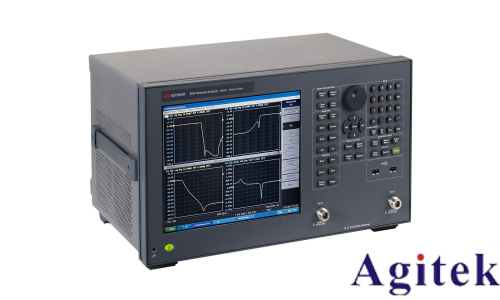

高頻探頭與矢量網絡分析儀的連接與阻抗測量方法

在高頻電路設計與測試中,阻抗匹配是確保信號完整性、降低反射和提升傳輸效率的關鍵環節。為了精確測量PCB焊盤在不同位置的阻抗變化,工程師常采用高頻探頭與矢量網絡分析儀(VNA)相結合的方式進行非破壞性測試。該方法不僅精度高,還能實時反映高頻信號下的阻抗特性,廣泛應用于高速數字電路、射頻模塊及高速接口(如PCIe 5.0)的設計驗證中。

一、設備連接與系統搭建

首先,需準備矢量網絡分析儀、高頻探針及待測PCB板。將網絡分析儀的測試端口(通常為50Ω標準接口)通過精密同軸電纜與高頻探針連接。高頻探針作為信號傳輸的“橋梁”,其探針尖端需精準接觸PCB焊盤的指定測試點。連接完成后,應檢查接頭是否牢固,避免因接觸不良引入額外損耗或反射。

二、儀器設置與校準

在正式測量前,必須對矢量網絡分析儀進行校準,以消除系統誤差。通常采用SOLT(短路-開路-負載-直通)校準法,在測試端口完成校準后,再連接探針進行“探針末端校準”(Probe Calibration),確保測量參考面準確移至探針尖端。隨后,設置合適的頻率范圍(如1GHz~20GHz)、掃描點數和輸出功率,以匹配被測信號的頻段需求。

三、焊盤阻抗實測與位置影響分析

以PCIE 5.0高速夾具為例,分別在焊盤的上方、中心和下方三個位置進行測試,觀察阻抗變化。測試發現:

焊盤上方:探針接觸點遠離連接器對接區域,形成較長的“stub”(短截線),引發顯著的寄生電感效應,導致測得阻抗偏低,實測值約為67.8Ω。該偏差源于stub引起的信號反射和阻抗失配。

焊盤中心:此位置為連接器標準對接區域,stub長度適中,信號路徑最接近理想狀態。測試結果顯示阻抗為86.3Ω,與設計值高度吻合,測量結果準確可靠,是推薦的測試位置。

焊盤下方:雖未在文中詳述,但依據傳輸線理論,若位置偏移仍可能引入不對稱結構,影響場分布,造成阻抗波動。

四、測量注意事項

1. 探針選擇:應根據測試頻率和焊盤間距(pitch)選用合適型號的高頻探針,確保其帶寬覆蓋測試頻段。

2. 接觸穩定性:調節探針架使探針保持水平,輕觸焊盤,觀察網絡分析儀S11曲線是否穩定,避免“跳針”或壓損焊盤。

3. 環境控制:測試應在屏蔽環境中進行,避免外部電磁干擾影響測量精度。

4. 重復驗證:對關鍵點進行多次測量,確保數據一致性。

結語

高頻探頭與矢量網絡分析儀的協同使用,為PCB阻抗測量提供了高精度解決方案。通過規范操作流程、精準定位測試點,并結合對測試位置影響的理解,工程師可有效提升測量準確性,為高速電路的阻抗匹配與信號完整性優化提供可靠數據支持。未來,隨著更高頻高速接口的發展,此類測量技術將愈發重要。

關注官方微信

關注官方微信